# **Environmental Data Exchange in Cooperating Driving Systems**

DatZZ001 Datorzinātņu doktorantūras zinātniskais seminārs

Aleksandrs Ļevinskis al17206

ELEKTRONIKAS UN DATORZINĀTŅU

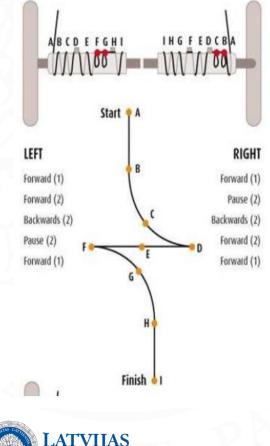

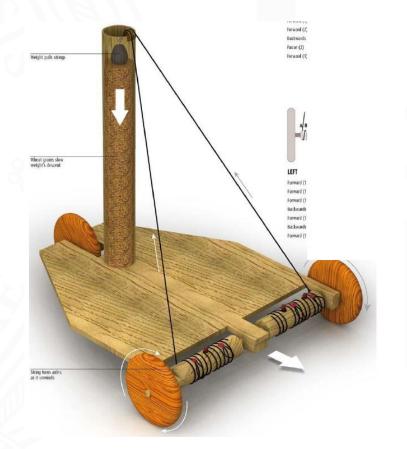

### First Ever Self Diving Vehicle

Greek inventor Hero's "Programmable Cart" AD60

# **PROMETHEUS** project

(lead by Daimlerchrysler Ag)

- PAN European project with 45 partners

- Project started in 1986 and finished in 1994

- 749 mil EUR funding

Working towards traffic without accidents: adaptive cruise control in testing as part of the PROMETHEUS research project

### Motivation

Lower human fatalities in accidents

Improve driving experience

Achieve autonomous driving

Make traffic more consistent

Improve intersection performance

Reduce emissions (green technology)

### First Ever Latvian Self Driving Car

- 2011 GCDC (Grand Cooperative Driving Challenge) participation in Helmond, Netherlands (Leo Selavo, Andris Gordjusins, Georgijs Kanonirs, Vadims Kurmis, Artis Mednis, Girts Strazdins and Reinholds Zviedris)

- 2016 GCDC participation

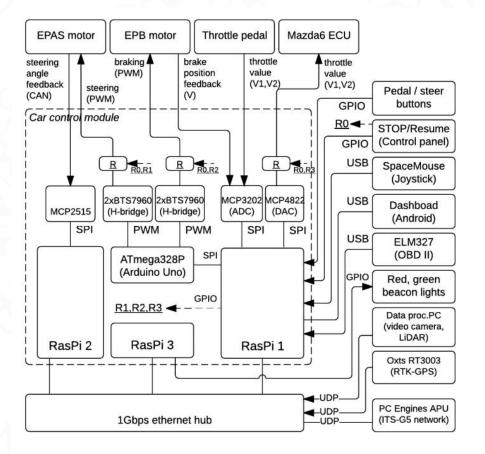

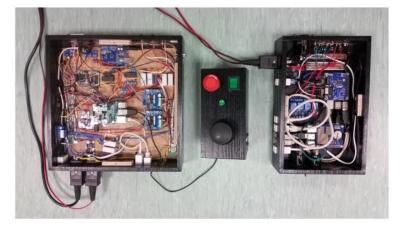

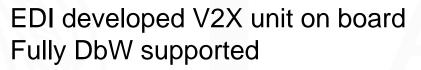

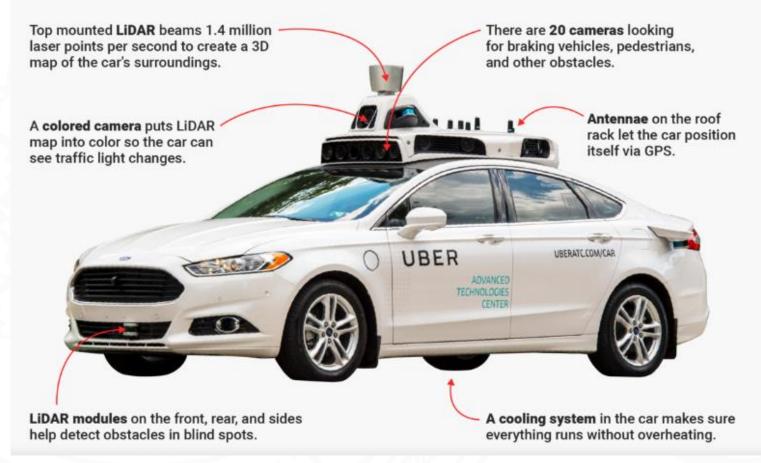

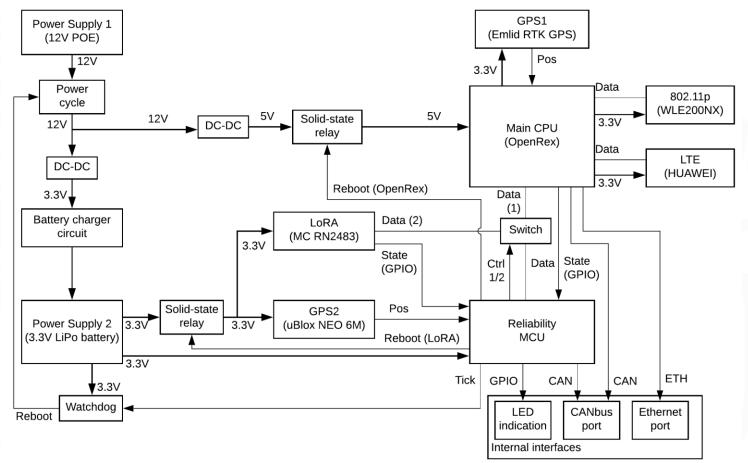

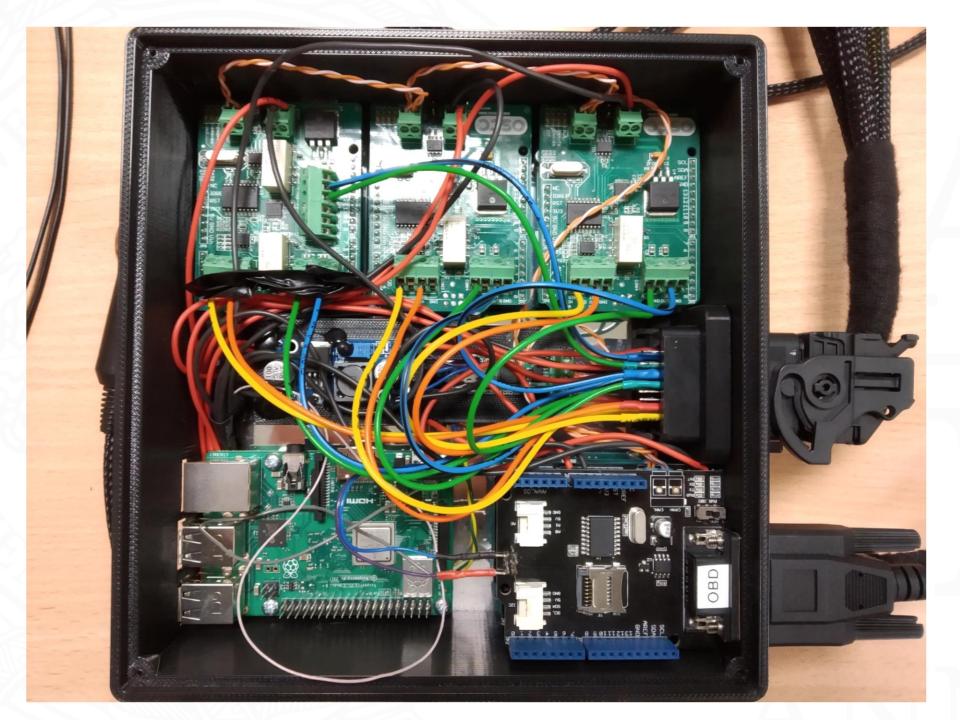

### Mazda6 arhitecture

ELEKTRONIKAS UN DATORZINĀTŅU INSTITŪTS

### **Current status**

- Based on 2018 Kia Soul EV

- Expected 5 radars, 12 cameras, LIDAR

- Nvidia PX2 DRIVE embedded intelegence

## **NVIDIA SDC**

# **NVIDIA SDC**

# **NVIDIA SDC**

# SAE Levels of Driving Automation

(in human language)

- Level 0 No Driving Automation

- You drive it

- Level 1 Driver Assistance

- Hands on the wheel

- Level 2 Partial Driving Automation

- Hands off the wheel, eyes on the road

- Level 3 Conditional Driving Automation

- Hands off the wheel, eyes off the road sometimes

- Level 4 High Driving Automation

- Hands, off, eyes off, mind off sometimes

- Level 5 Full Driving Automation

- Steering wheel is optional

### SAE Levels of Driving Automation (in SAE J 3016-2018\* words)

| ODD         | Operational Design Domain                                   | LDW<br>BSW        | Lane Departure Warning<br>Blind Spot Warning                                        |  |  |

|-------------|-------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------|--|--|

| ADS<br>SAE  | Automated Driving System<br>Society of Automotive Engineers | ABS<br>ESC<br>ACC | Anti-lock Braking System<br>Electronic Stability Control<br>Adaptive Cruise Control |  |  |

| DDT<br>OEDR | Dynamic Driving Task<br>Object and Event detection and      |                   |                                                                                     |  |  |

| Response    |                                                             |                   |                                                                                     |  |  |

\*Taxonomy and Definitions for Terms Related to Driving Automation Systems for On-Road Motor Vehicles.

### SAE Levels of Driving Automation (in SAE J 3016-2018\* words)

### SAE Levels of Driving Automation (in SAE J 3016-2018\* words)

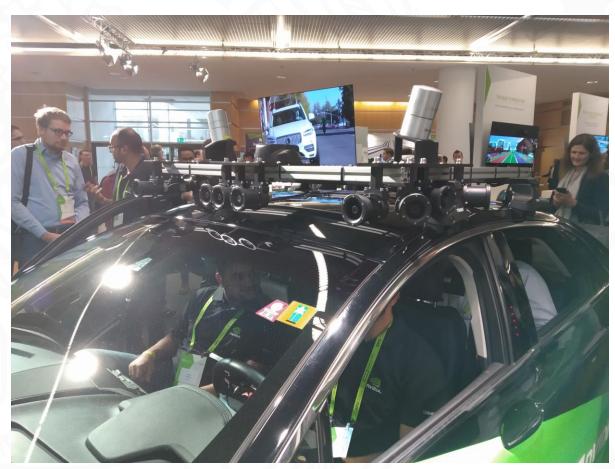

### **Self-Driving Cars Nowadays**

# **Self-Driving Cars Nowadays**

- Environment perception (LIDAR, RADAR, CAMERA, e.t.c)

- Embedded Intelligence (PC ROS, NVIDIA DRIVE PLATFORM)

- Communication (V2X, C-V2X, DSRC)

- Navigation (GNSS, RTK)

- Localization and Maping (SLAM)

- Actuation (DbW Steering, Brakig, Shifting, Acceleration)

#### Environment perception CAMERA

- RCCB camera better SNR, Dynamic range

- RAW data over GMSL (GIGABIT MULTIMEDIA SERIAL LINK) interface 1.6Gbps or 3.12Gps

| Pattern                    | Bayer RG/GB | 25%C           | 50%C:<br>RG/BC<br>Pattern A | 50%C:<br>RG/BC<br>Pattern B | 50%C:<br>RC/CB<br>Clarity+ |

|----------------------------|-------------|----------------|-----------------------------|-----------------------------|----------------------------|

| Unit cell                  | 2 x 2       | 2 x 2          | 4 x 4                       | 4 x 4                       | 2 x 2                      |

| SNR improvement            | 0 dB (ref.) | 1 dB           | 3-4 dB                      | 3-4 dB                      | 3-4 dB                     |

| Sharpness                  | reference   | lower          | slightly lower              | slightly lower              | equivalent                 |

| Spatial color<br>artifacts | reference   | slightly worse | serious                     | serious                     | equivalent                 |

Table 1. Summary of commonly used and proposed Color Filter Array (CFA) patterns including Clarity+ RC/CB

Figure 1. Motivation for Clear: because they span the visible spectrum, Clear pixels collect 2X more signal than Green pixels.

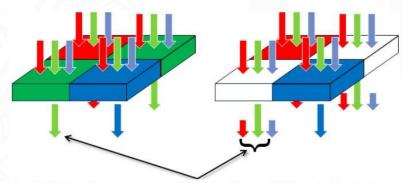

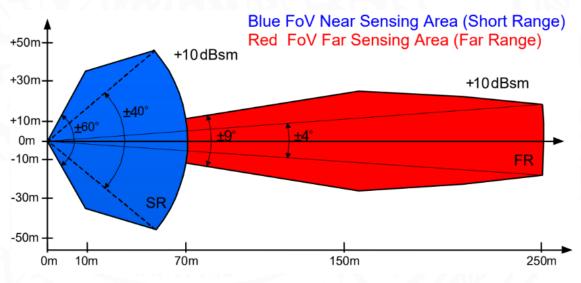

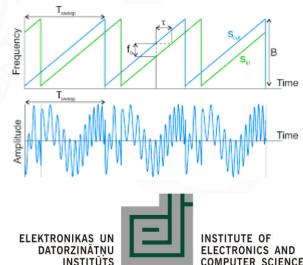

#### **Environment perception** RADAR

- **RA**dio Detection And Ranging •

- CAN2.0 500kbps •

- Filtered Cluster Data •

LATVIJAS

ΟF

LATVIA

UNIVERSITY

Frequency Modulated Continuous Wave

COMPUTER SCIENCE

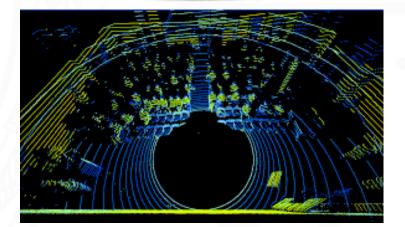

# Environment perception

- Light Imaging, Detection And Ranging

- HDL-32E 32 laser LIDAR

- 100BASE T ETHERNET

- Broadcasting UDP packets with particular Laser and Sector distance

- +10° to -30° Vertical FOV

- 80m-100m Range

- ± 2 cm Accuracy

- Up to ~1.39 Million Points per Second

INSTITUTE OF ELECTRONICS AND COMPUTER SCIENCE

# **Embedded Intelligence**

# **Embedded Intelligence**

# **Embedded Intelligence**

| Nvidia provided<br>reference board | Drive CX                              | Drive PX                              | Drive PX 2<br>(AutoCruise)                             | Drive PX 2<br>(Tesla)                                                                 | Drive PX 2<br>(AutoChauffeur)                                                                           | Drive PX2 (Tesla 2.5)                                            | Drive PX Xavier <sup>[15]</sup>                                                                | Drive PX Pegasus <sup>[20]</sup>                         |

|------------------------------------|---------------------------------------|---------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| GPU<br>Microarchitecture           | Maxwell (28 nm)                       |                                       | Pascal (16 nm)                                         |                                                                                       |                                                                                                         | Volta (12 nm)                                                    |                                                                                                |                                                          |

| Introduced                         | January 2015                          |                                       | September 2016 <sup>[21]</sup>                         | October 2016 <sup>[22]</sup>                                                          | January 2016                                                                                            | August 2017 <sup>[23]</sup>                                      | January 2017                                                                                   | October 2017                                             |

| Computing                          | 1x Tegra X1                           | 2x Tegra X1                           | 1x Tegra X2 (Parker)<br>+ 1x Pascal GPU                |                                                                                       | 2x Tegra X2 (Parker)<br>+ 2x Pascal GPU                                                                 | 2x Tegra X2 (Parker)<br>+ 1x Pascal GPU <sup>[24]</sup>          | 1x Tegra Xavier <sup>[25]</sup>                                                                | 2x Tegra Xavier                                          |

| CPU                                | 4x Cortex<br>A57<br>4x Cortex<br>A53  | 8x Cortex<br>A57<br>8x Cortex<br>A53  | 2x Denver<br>4x Cortex A57                             |                                                                                       | 4x Denver<br>8x Cortex A57                                                                              | 4x Denver<br>8x Cortex A57                                       | 8x NVIDIA Custom Carmel<br>ARM64 <sup>[25]</sup>                                               | 16x NVIDIA Custom Carmel<br>ARM64                        |

| GPU                                | 2 SMM<br>Maxwell<br>256 CUDA<br>cores | 4 SMM<br>Maxwell<br>512 CUDA<br>cores | 1x Parker GPGPU<br>(1x 2 SM Pascal, 256 CUDA<br>cores) | 1x Parker GPGPU<br>(1x 2 SM Pascal, 256 CUDA cores on a<br>MXM slot <sup>[11]</sup> ) | 2x Parker GPGPU<br>(2x 2 SM Pascal, 512 CUDA<br>cores)<br>+ 2x dedicated MXM<br>modules <sup>[26]</sup> | 1x Parker GPGPU<br>1x 2 SM Pascal, 256 CUDA cores<br>[23][24]    | 1x Volta iGPU (512 CUDA<br>cores) <sup>[25]</sup>                                              | 2x Volta iGPU (512 CUDA<br>cores)<br>2x post-Volta dGPUs |

| Accelerator                        |                                       |                                       |                                                        |                                                                                       |                                                                                                         |                                                                  | 1x DLA <sup>[25]</sup>                                                                         | 2x DLA                                                   |

| Memory                             |                                       |                                       | 8GB LPDDR4 <sup>[27]</sup>                             |                                                                                       | 16GB LPDDR4 <sup>[27]</sup>                                                                             |                                                                  | LPDDR4 <sup>[25]</sup>                                                                         |                                                          |

| Storage                            |                                       |                                       | 64GB eMMC <sup>[27]</sup>                              |                                                                                       | 128GB eMMC <sup>[27]</sup>                                                                              |                                                                  |                                                                                                |                                                          |

| Performance                        |                                       |                                       | 4 FP32 TFLOPS<br>10-12 DL TOPS <sup>[28][29]</sup>     | 4 FP32 TFLOPS<br>10-12 DL TOPS <sup>[28][29]</sup>                                    | 16 FP16 TFLOPS<br>8 FP32 TFLOPS<br>20-24 DL TOPS <sup>[28][29]</sup>                                    | 4 FP32 TFLOPS<br>10-12 DLTOPS <sup>[28][29]</sup>                | 20 INT8 TOPS, 1.3 FP32 TFLOPS<br>(GPU)<br>10 INT8 TOPS, 5 FP16 TFLOPS<br>(DLA) <sup>[25]</sup> | 320 INT8 TOPS (total) <sup>[30]</sup>                    |

| TDP                                |                                       | 20W <sup>[29]</sup>                   | 40W<br>SoC portion: 10 W <sup>[21]</sup>               | 40W<br>SoC portion: 10 W <sup>[21]</sup>                                              | 80W <sup>[31][32][29][33]</sup><br>SoC portion: 20 W <sup>[21]</sup>                                    | 60W <sup>[31][32][29]</sup><br>SoC portion: 20 W <sup>[21]</sup> | 30W <sup>[25]</sup>                                                                            | 500W <sup>[30]</sup>                                     |

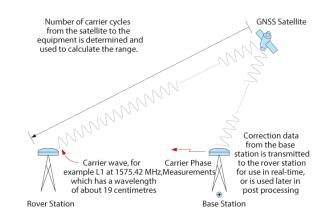

# GNSS, RTK

- GPS/QZSS L1, GLONASS G1, BeiDou B1, Galileo E1, SBAS

- Static: H: 5mm + 1ppm, V: 10mm + 2ppm

- Kinematic: H: 7mm + 1ppm, V: 14mm + 2ppm

- IMU: 9DOF

- Update rate:14 Hz / 5 Hz

Figure 42 Real-Time Kinematic

# V2X, DSRC

### V2X, DSRC

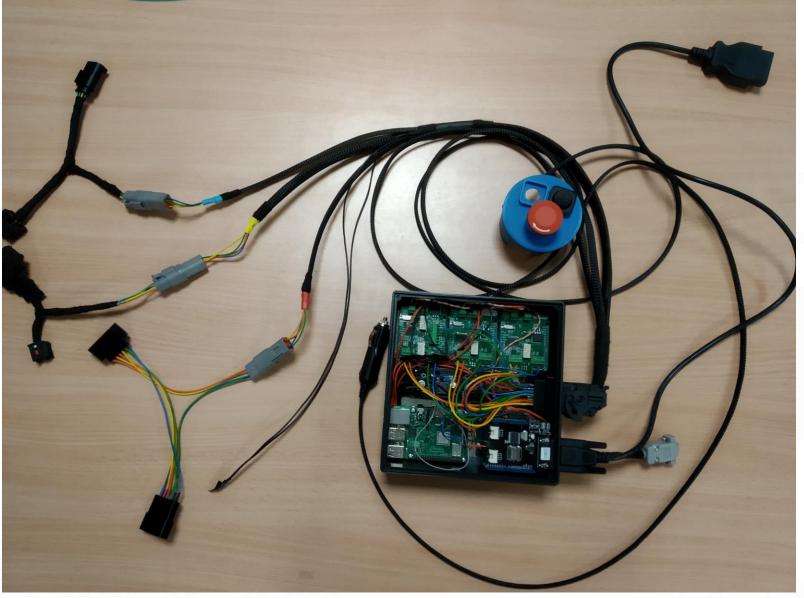

# **DbW** unit

Spliced wires to be lengthened

with alternate colors for clarity

### Main Thesis Motivation

There are self driving cars already exists and participating in traffic . However they are individual units. There is certain risk for mismatch data exploit for active sensor, like LIDAR or RADAR if many self-driving cars will appear in the same area.

• Using V2V it will be possible to efficiently control channels for such active sensors.

Still the vast of the majority of vehicles doesn't has connecting capability, by enabling fully-equipped vehicles (with V2V unit and Environmental Perception Capabilities) exchange environmental data (what it observes) it is possible to eliminate such problem.

### Main Thesis Motivation (cont.)

Detection and data propagation about VRUs (Vulnerable Road Users) such as cyclist, pedestrian ...

Better representation of road scene, which can be used for optimized path planning and emergency scenarios execution.

## Work in progress...

- Realiable communication, with current prototype.

- PX2 platform deployment (DriveNet, OEDR)

- NS-3 simulations with different conditions.

- Article review

### **Upcoming publications**

LoRa modulation TDMA based Physical Layer Management Entity (PLME) in cooperative vehicular applications.

# Acknowledgment Auto Dri?e

H2020 ECSEL project "Advancing fail-aware, fail-safe, and failoperational electronic components, systems, and architectures for highly and fully automated driving to make future mobility safer, more efficient, affordable, and end-user acceptable" (AUTODRIVE)

(AUTODRIVE Granta līguma Nr. 737469), skatīt <u>www.autodrive-</u> project.eu/

**Ilgums:** 36 mēneši (2017 - 2020) **Partneri:** 58 partneri no 13 valstīm.

ELEKTRONIKAS UN DATORZINĀTŅU INSTITŪTS

Programmable Systems for Intelligence in Automobiles (PRYSTINE)

(**PRYSTINE** Granta līguma Nr. 783190) **Ilgums:** 36 mēneši (2018 - 2021) **Partneri:** 60 partneri no 14 valstīm.

# OUR TEAM

- Modris Greitāns (Dr. Sc. Comp.)

- Roberts Kadiķis (Dr.Sc.Ing)

- Ingars Ribners (Ms. Sc. Comp.)

- Gatis Gaigals (Ms. Sc. Ing)

- Daniels-Jānis Justs (Ms. Sc. Ing)

- Kaspars Ozols (Dr.Sc.Ing)

- Aleksandrs Ļevinskis (Ms. Sc. Ing)

- Rihards Novickis (Ms. Sc. Ing)

- Juris Ormanis (Bs. Sc. comp)

- Vitalijs Fescenko (Bs. Sc. Comp.)

### Thank you for attention!